返回上层

PLC晶圆

ITEM | Pitch | Commodity & Des | ||||||

Dimensions(mm) | Effective figures | Premium Grade Chip | ||||||

Yieid(%) | Effective figures | Optical Specifications | ||||||

1×2 Channel | Full(250um) | W(±0.2) | 1.80 | 800 | 90% | 720 | I.L | 3.5dB |

1×4 Channel | Full(250um) | W(±0.2) | 2.30 | 580 | 90% | 522 | I.L | 6.7dB |

1×8 Channel | Full(250um) | W(±0.2) | 2.30 | 450 | 90% | 405 | I.L | 9.8dB |

1×8 Channel | Half(127um) | W(±0.2) | 2.30 | 570 | 90% | 513 | I.L | 9.8dB |

1×16 Channel | Half(127um) | W(±0.2) | 2.60 | 330 | 85% | 280 | I.L | 13.0dB |

1×32 Channel | Half(127um) | W(±0.2) | 4.50 | 150 | 80% | 120 | I.L | 16.2dB |

1×64 Channel | Half(127um) | W(±0.2) | 9.30 | 49 | 75% | 37 | I.L | 19.5dB |

2×16 Channel PLC Splitter Wafer | Half(127um) | W(±0.2) | 2.60 | 230 | 75% | 172 | I.L | 13.5dB |

2×32 Channel PLC Splitter Wafer | Half(127um) | W(±0.2) | 4.50 | 110 | 75% | 82 | I.L | 17.0dB |

设备

全系列采用日韩进口设备

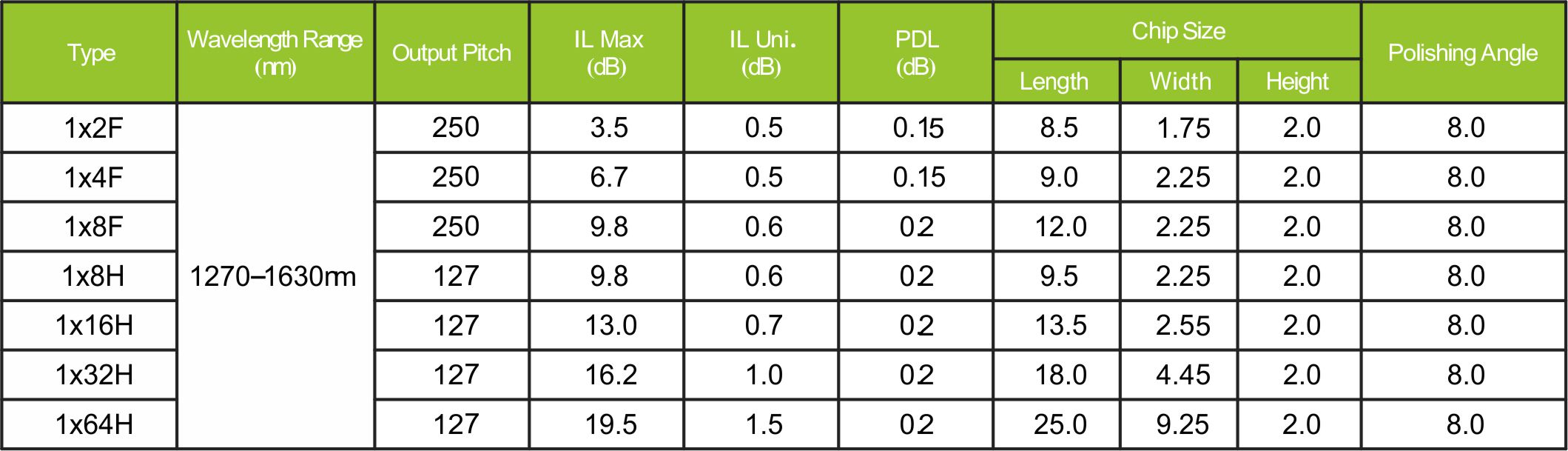

1xn PLC Splitter Chip

Specifications:

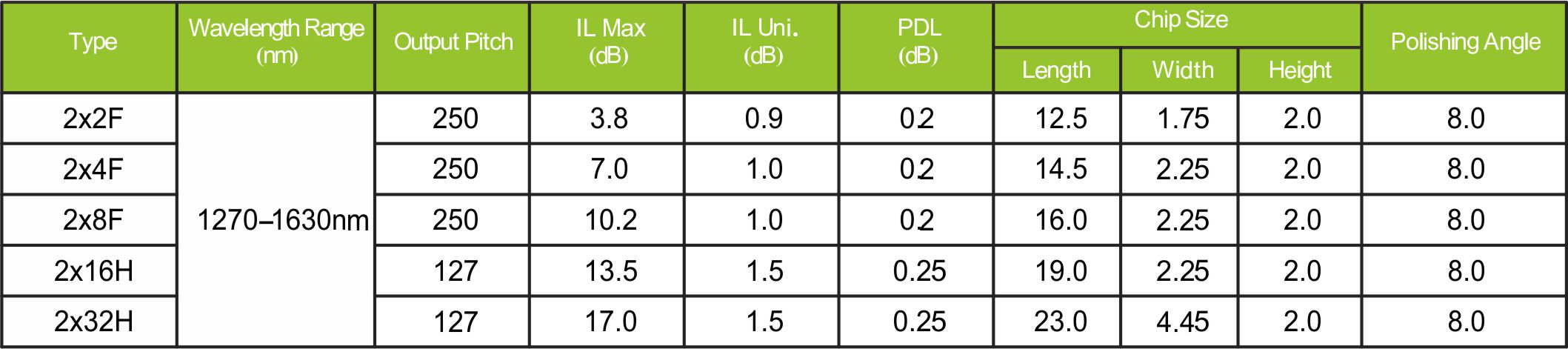

2xn PLC Splitter Chip

Specifications:

PLC Splitter Chip光学特性

Specifications:

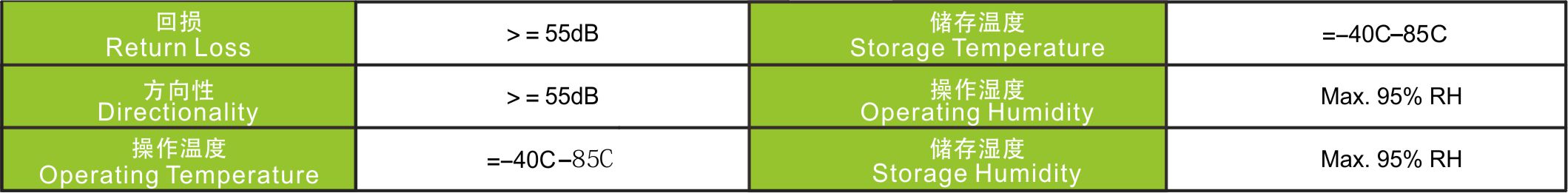

芯片PCT测试

芯片PCT(Pressure Cooker Test)测试,采用业界最严谨的测试条件,

确保芯片胶合制程之稳定性,条件如下:

湿度:100%

温度:120℃

压力:0.11MPa

时间:99个小时

Oven:100℃ 60分钟

前处理:无

UV硬化:10分钟

Epoxy量:0.7g

无水分穿透现象